| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | ||||||

| 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| 16 | 17 | 18 | 19 | 20 | 21 | 22 |

| 23 | 24 | 25 | 26 | 27 | 28 |

- oxidation

- Energy Band

- SOI MOSFET

- effective mass

- 반도체 8대공정

- Short Channel Effect

- Warpage

- finFET

- 양자역학

- Threshold Voltage

- Dynamic Random Access Memory

- She

- Punch through

- 반도체공정

- mechanism

- feol

- RCAT

- 반도체공학

- 부피결함

- DRAM

- 반도체소자

- MOSFET

- ion implantation

- Silicon on Insulator

- HBM

- GIDL

- doping

- high bandwidth memory

- 선결함

- SK하이닉스

- Today

- Total

반도체 공부 기록

[반도체소자] 10. Gate leakage current 본문

Gate leakge current

반도체 소자는 Moore's law에 따라 소자의 크기가 작아지고, 집적도는 향상되었습니다. 소자 미세화에 따라 Channel length가 짧아져서 Short channel effect가 발생하여 소자의 performance를 감소시켰습니다. 이번 포스팅에서는 소자 미세화에 따라서 Capacitance의 증가가 요구되어 Gate oxide thickness의 감소에 따른 Issue를 알아보도록 하겠습니다.

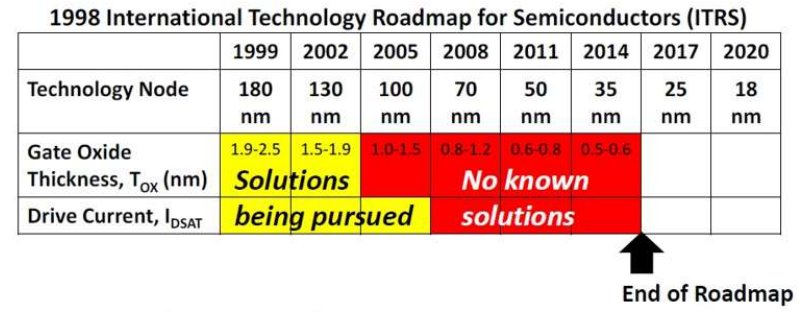

1998년 ITRS의 로드맵에 따르면 Technology node가 100nm 이하로 진입하게 되는 경우 Gate oxide thickness가 1nm 이하로 요구되었습니다. 하지만 1nm 이하의 두께를 가지는 Gate oxide를 MOSFET에 적용하게 되는 경우 Gate leakage current가 발생하는 문제가 있었습니다. Gate laekage current는 얇아진 Gate oxide를 통해 Channel 영역에 존재하는 전자가 Tunneling에 기인합니다. Gate leakage current는 소자의 Power consumption을 초래하기 때문에 반드시 방지해야합니다.

♭ Tunneling

Tunnneling은 전자가 Gate oxide(Dielectric)을 직접 통과하는 현상을 말합니다.

1. Direct tunneling

Direct tunneling은 전기장을 인가하면 전자가 얇은 두께를 가지는 Gate oxide(Dielectric)을 통과하는 현상입니다.

Direct tunneling에 의한 Current density는 Gate oxide thickness(tox)에 관한 함수로 tox가 감소할수록 Direct tunneling current density는 기하급수적으로 증가합니다. → Gate oxide의 두께에 따라 Tunneling current 결정

2. FN(Fowler-Nordheim) tunneling

FN(Fowler-Nordheim) tunneing은 인가된 전기장에 의해 Gate oxide(Dielectric)의 Energy band banding에 따라 Tunneling width(Energy barrier)가 감소하여 전자가 Gate oxide(Dielectric)을 통과하는 현상입니다.

FN tunneling에 의한 Currnet density는 Electric field(Etun)에 관한 함수로 Etun이 증가할수록 FN tunneling current density가 기하급수적으로 증가합니다. → 전기장의 크기에 따라 Tunneling current 결정

일반적으로 Direct tunneling current density는 FN tunneling current density보다 100~1000배 큰 특징을 가지고 있습니다.

(Tunneling은 Flash memory의 작동원리로 사용됩니다. 이때 Direct tunneling은 낮은 효율을 가지지만 큰 전류를 만들 수 있고, FN tunneling은 높은 효율을 가지지만 작은 전류를 만드는 특징이 있습니다. '낮은 효율을 가지지만 큰 전류?, 높은 효율을 가지지만 작은 전류?'라는 문장이 어색할 수 있습니다. 예를 들어 설명하면, Direct tunneling은 1억개 중 1%의 전자가 Tunneling에 기여하고, FN tunneling은 100개 중 99%의 전자가 Tunneling에 기여합니다. 그렇다면 Direct tunneling의 효율은 1% 이지만 1000만개의 전자에 의해 전류가 생성되고, FN tunneling의 효율으 99%이지만 99개의 전자에 의해 전류가 생성됩니다.)

♭ Solution

전력 낭비를 방지하기 위해 Gate leakage current(특히 Direct tunneling current)는 반드시 방지해야 합니다. 소자 미세화에 따라 Short channel effect를 막기 위하여 Gate controllability(게이트 통제력)을 증가시키기 위해 Capacitance의 증가가 요구되고 있습니다. 하지만 Capacitance를 증가시키기 위해 Gate oxide thickness를 무한정 줄이게 된다면 Direct tunneling이 기하급수적으로 증가하여 Gate leakage current가 발생합니다.

Tunneling을 방지하기 위해서 더 이상 두께를 줄이지 못하기 때문에 높은 유전상수(High-K)를 가지는 물질들을 Gate oxide에 기존 MOSFET의 Gate oxide인 SiO2를 대신하여 적용합니다. 그렇다면 상대적으로 두꺼운 두께를 가지더라도 Capacitance를 증가시킬 수 있기 때문에 Gate controllability는 증가하지만 Gate leakage current는 통제할 수 있습니다.

♭ High-K Materials

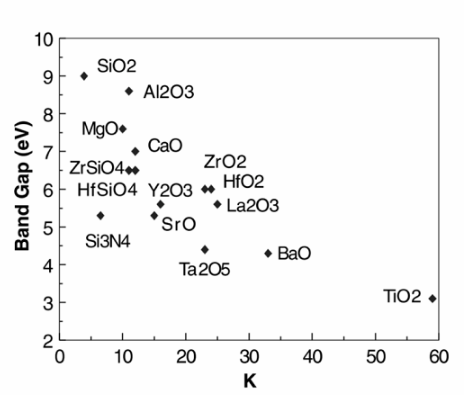

높은 유전상수를 가지게 되면 Gate capacitance가 증가하기 때문에 Gate controllability가 증가하여 Short channel effect를 효과적을 제어할 수 있습니다. 하지만 Gate oxide를 High-K(ZrO2, HfO2) 물질을 적용하는 경우에도 단점은 존재합니다. High-K 물질은 Conduction band offset(ΔEc)이 매우 작아 기판(p-Silicon) 영역의 Free electron이 Energy barrier 넘어 Gate cuurent를 형성하는 문제가 발생할 수 있습니다. High-K 물질을 사용하기 위해서는 ΔEc가 1eV 이상이 요구됩니다.

따라서, MOSFET에서는 높은 유전상수를 가지면서 Bandgap(Conduction band offset)이 큰 물질을 적용해야합니다.

♭ 유전상수(Dielectric constant) VS 밴드갭(Bandgap)

일반적으로 유전상수와 밴드갭은 반비례 관계를 가지고 있습니다. 유전상수와 밴드갭은 모두 Atomic bonding 세기에 영향을 받습니다. Atomic bonding 강할수록 이웃한 원자 사이 거리가 좁습니다.

먼저, Energy band를 형성할 때 원자 상태에서 가지고 있던 에너지 준위가 파울리 배타원리에 의해 Spliting이 발생하고 이에 따라 에너지 준위가 존재하지 않는 영역의 크기를 밴드갭이라고 한다. 이때 Atomic bonding이 강할수록 원자들이 접근하면서 에너지 준위가 더 큰 간격을 가지고 Spliting이 발생하여 큰 밴드갭을 갖게 된다.

유전상수는 클수록 분극(Polarization)이 잘 발생하고 반대로 작을수록 분극이 적게 발생합니다. 따라서 유전상수가 큰 물질일수록 분극이 잘 발생하여 Gate에 인가된 전압을 Field effect에 의해 잘 전달할 수 있습니다. 유전상수는 Atomic bonding이 큰 물질일수록 작은 특성을 가지고 있습니다. Atomic bonding이 강하다는 것은 원자와 원자 사이의 Interaction이 강하게 작용하고 있어 외부 전기장에 의해 분극이 잘 발생하지 않습니다.

♭ High-K issue

High-K 물질을 적용하게 되는 경우 앞서 설명드린 Bandgap에 관련한 문제말고도 다양한 이슈가 존재하여 다음과 같은 특성이 요구됩니다.

1) 열적 안정성(Themal stability)

High-K 물질은 비교적 낮은 온도(400~500℃)에서 결정화가 이루어집니다. 결정화가 진행되면 결정립계(Grain boundary)가 형성되는데, 이 결정립계는 전자가 이동할 수 있는 경로를 제공하게 됩니다. 즉, 전자가 High-K의 결정립계를 따라 이동하면서 전류를 형성하게 되므로 우수한 열적 안정성을 가지는 High-K 물질을 적용해야합니다.

2) 계면 품질(Interfacial quality)

기존 MOSFET의 경우 Gate oxide를 SiO2를 사용하기 때문에 기판 물질인 Si와의 계면 특성이 매우 우수하였습니다. 하지만 High-K 물질과 Si의 계면에서 Trap site가 형성되어 전자가 Trap 되는 경우 MOSFET의 Threshold voltage modulation이 발생할 수 있으므로 계면 품질이 우수한 High-K 물질을 적용해야합니다.

3) 공정 적합성(Process compatibility)

High-K 물질을 Gate oxide에 적용하기 때문에 균일한 두께 제어가 요구된다. 따라서 ALD, CVD를 통해서 증착하기 위해서 적당한 Precursor를 가지는 High-K 물질이면서, 결정화를 방지하기 위해 낮은 온도에서 증착이 가능한 공정을 사용해야 한다.

<출처>

Donald A. Neaman, "Semiconductor physics and device" 4th edition.

International Technology Roadmap for Semiconductor(ITRS)

J. Robertson, "Band offsets of wide-band-gap oxides and implications for future electronic devices", J. Vac. Sci. Tech. B, 18 (2000) 1785.

오류가 있다면 지적해주시면 감사하겠습니다 :)

'반도체소자' 카테고리의 다른 글

| [반도체소자] 12. SOI MOSFET (2) (0) | 2023.07.05 |

|---|---|

| [반도체 소자] 11. SOI MOSFET (1) (0) | 2023.07.04 |

| [반도체소자] 9. Body effect(Substrate bias effect) (0) | 2023.06.27 |

| [반도체소자] 8. Hot Carrier Injection(HCI) (1) | 2023.06.25 |

| [반도체소자] 7. Gate Induced Drain Leakage(GIDL) (0) | 2023.06.23 |