| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | ||||||

| 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| 16 | 17 | 18 | 19 | 20 | 21 | 22 |

| 23 | 24 | 25 | 26 | 27 | 28 |

- 선결함

- 반도체 8대공정

- SK하이닉스

- She

- effective mass

- 반도체공학

- GIDL

- Punch through

- Short Channel Effect

- 부피결함

- doping

- Threshold Voltage

- Dynamic Random Access Memory

- feol

- finFET

- Warpage

- ion implantation

- Energy Band

- 반도체소자

- DRAM

- SOI MOSFET

- 반도체공정

- MOSFET

- Silicon on Insulator

- oxidation

- HBM

- RCAT

- high bandwidth memory

- 양자역학

- mechanism

- Today

- Total

반도체 공부 기록

[반도체소자] 20. SRAM 본문

SRAM(Static Random Access Memory)

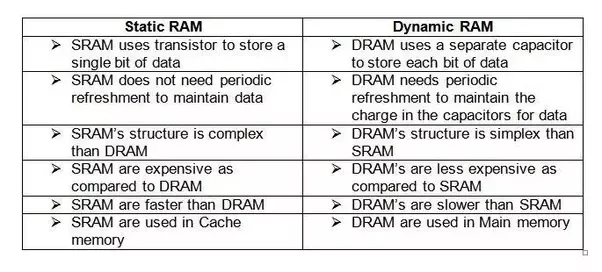

Static Random Access Memory(SRAM)의 'Static'은 '정적인' 의미를 가지고 있습니다. SRAM의 '정적인'의 의미는 Filp-flop 방식으로 전류 신호가 오기 전까지는 상태가 변화하지 않기 때문입니다. 전원이 연결되어 있는 경우 시간의 경과에 따라서 정보가 소멸, 변화하지 않기 때문에 안정적인(정적인) 메모리 소자입니다. (DRAM과 같이 정보를 유지하기 위해서 별도의 "REFRESH" 동작이 요구되지 않습니다.) SRAM도 RAM의 한 종류으로 휘발성 메모리이므로 전원을 차단시키면 SRAM에 저장되어 있는 정보는 모두 사라지게 됩니다.

반면, Dynamic Random Access Memory(DRAM)의 'Dynamic'은 '동적인' 의미를 가지고 있습니다. DRAM은 '동적인'의 의미는 Capacitor 방식으로 Selected transistor에 의한 Leakage current에 의해 Charge가 손실되기 때문입니다. 전원이 연결되어 있음에도 불구하고 시간의 경과에 따라서 정보가 소멸, 변화하기 때문에 Refresh 동작이 반드시 필요한 메모리 소자입니다.

SRAM은 DRAM에 비해 빠른 동작 속도를 가지기 때문에 CPU 내부의 기억 장치(Cache memory 등)와 같이 속도를 중요시하는 부분에서 많이 사용합니다. SRAM은 DRAM과 다르게 Refresh 동작이 요구되지 않기 때문에 nano-seconds 단위로 Access가 가능하기 때문입니다. (DRAM은 Access에 50~80ns 시간이 소요됩니다.) 일반적인 SRAM의 경우 6개의 Transistor(2개의 Transistor + 2개의 Inverter)로 구성되어 있어 DRMA에 비해 복잡한 구조를 가지기 때문에 집적도가 떨어지고, 이에 따라서 DRAM에 비해 가격이 비쌉니다.

♭ Inverter

SRAM의 동작 원리를 파악하기 위해서는 Inverter의 동작 메커니즘에 미리 알아야합니다. Inverter는 2개의 MOSFET으로 구성되어 있습니다. Inverter logic gate를 수행하기 위해서 PMOS를 통해 Pull-up network를 형성하고 NMOS를 통해 Pull-down network를 형성합니다. NMOS에는 GND와 연결되어 있고, PMOS는 VDD에 연결되어 있습니다.

A(Input)에 V = 0 ("0" signal)이 인가되는 경우 PMOS가 Turn-on 되어 VDD에 의해 Y(Output)이 "1" 으로 출력(Cout charging)됩니다. 반대로, A(Input)에 V = VDD ("1" signal)이 인가되는 경우 NMOS가 Turn-on 되어 GND에 의해 Y(Output)이 "0"으로 출력(Cout discharging)됩니다.

| Pull-up network OFF | Pull-up network ON | |

| Pull-down network OFF | Z | 1 |

| Pull-donw network ON | 0 | Crowbarred(X) |

Inverter에서 Pull-up/Pull-down network가 모두 OFF 되어있는 경우는 높은 저항으로 작용하며, 모두 ON되어 있는 경우 전력 낭비(Inverter 기능을 수행하지 못하고 전력만 사용)하는 상태가 되어 허용될 수 없습니다.

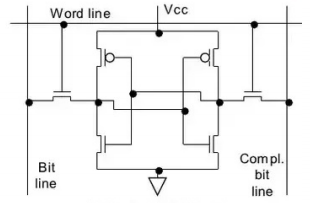

♭ 6T SRAM

가장 일반적인 SRAM의 형태로 6개의 Transistor가 있고, 6개의 Transistor 중 2개는 Selected transistor로 4개는 CMOS inverter logic gate으로 구성되어 있습니다.

1. Data 저장 장소, 저장하는 물리량

Inverter chain state를 Inverter에 저장하여 Data(0/1)을 구분합니다.

2. Write 방식

| "1" WRITE | "0" WRITE |

| ① WL에 VDD(≥ VTH) 인가 → 2개의 Transistor(Switch) turn-on ② BL = VDD, /BL = 0 인가 ③ Right inverter state = "0", Left inverter state = "1" |

① WL에 VDD(≥ VTH) 인가 → 2개의 Transistor(Switch) turn-on ② BL = 0, /BL = VDD 인가 ③ Right inverter state = "1", Left inverter state = "0" |

|

|

3. Read 방식 → Destructive read

Inverter chain state를 직접적으로 Bit line를 통해 전압, 전류 변화를 통해서 정보를 읽는 방식으로 Destructive read 방식입니다.

| "1" READ | "0" READ |

| ① WL에 VDD(≥ VTH) 인가 → 2개의 Transistor(Switch) turn-on ② Output: BL = 0, /BL = VDD 인가 ③ Sense amplifer로 ΔVB sensing |

① WL에 VDD(≥ VTH) 인가 → 2개의 Transistor(Switch) turn-on ② Output: BL = VDD, /BL = 0 인가 ③ Sense amplifer로 ΔVB sensing |

|

|

♭ 4T SRAM

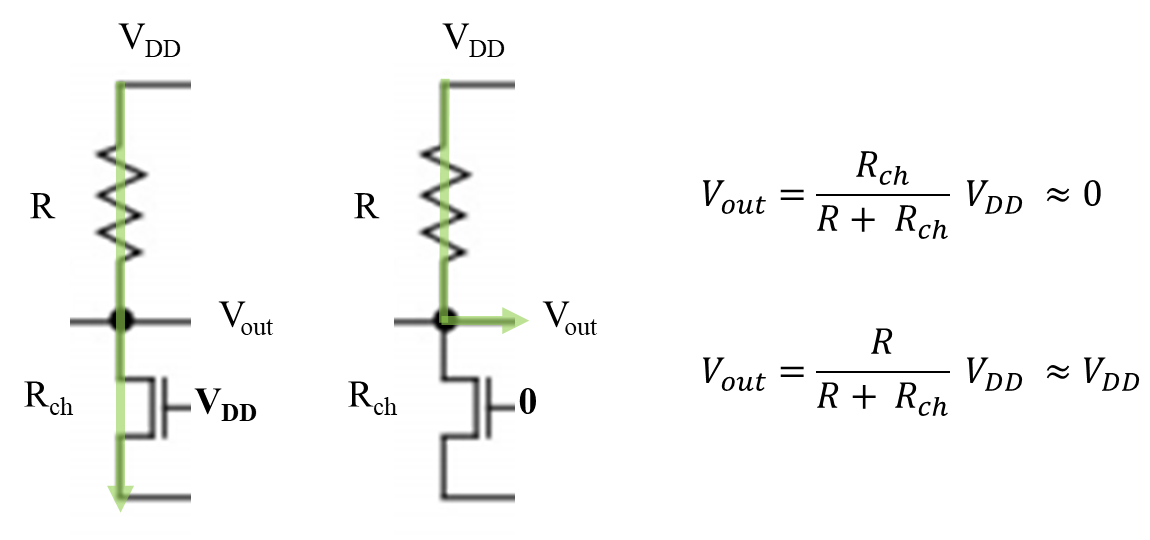

4T SRAM은 가장 일반적인 6T SRAM에서 2개의 Transistor가 빠진 구조입니다. SRAM을 구성하고 있는 2개의 Inverter (CMOS)의 PMOS 대신 '저항(Poly-load resistor)'으로 대체되어 있습니다. Inverter의 PMOS 대신 저항을 사용하기 때문에 Stanby current가 높습니다. 또, Noise에 민감하며 Soft error rate가 높은 단점이 있습니다. Write, Read 방식은 6T SRAM과 동일합니다.

전압 분배 법칙에 따라 NMOS에 인가되는 전압에 따라 Vout 값이 상이하게 되어 구분되는 값을 도출할 수 있습니다. 4T SRAM을 동작하는 경우 NMOS에 전압이 인가되는 경우 Vout은 "0"의 값으로 수렴합니다. 하지만 4T SRAM에서 PMOS 대신에 Resistor를 적용하기 때문에 CMOS inverter를 사용하는 경우보다 높은 값(≥ 0)을 가집니다. Inverter chain state를 직접적으로 Bit line의 전압, 전류 변화를 통해서 읽기 때문에 Destructive read 방식입니다.

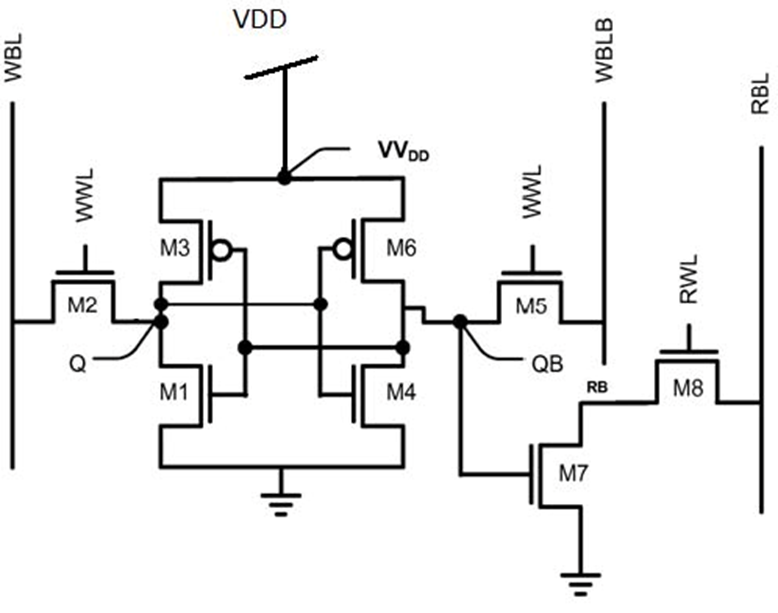

♭ 8T SRAM

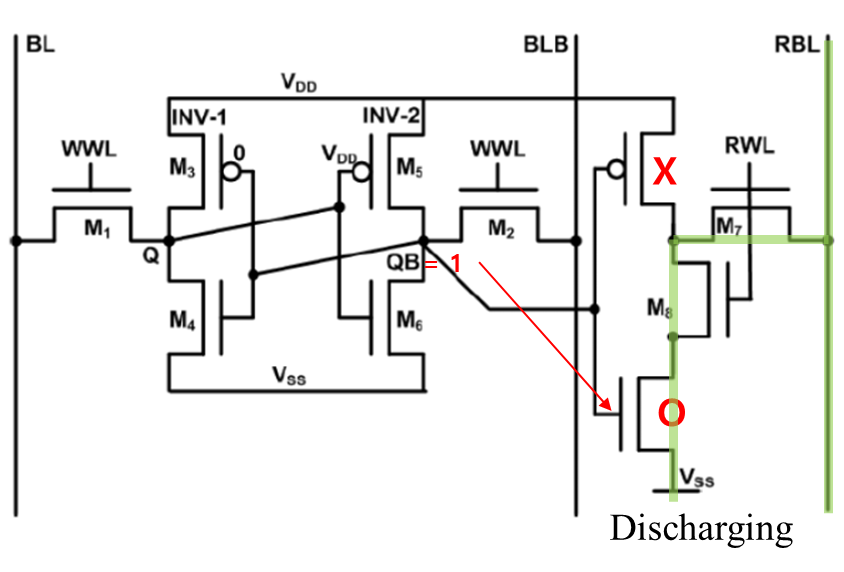

8T SRAM은 가장 일반적인 6T SRAM에서 2개의 추가적인 Transistor(NMOS)를 추가한 구조를 가지고 있습니다. 6T SRAM과 다르게 Read-port(Read buffer)로 사용되는 M7, M8을 통해서 Cell과 De-coupling을 통해 독립적으로 작동합니다. 8T SRAM은 M7, M8을 추가하여 Read-port를 통해서 6T SRAM의 Static noise margin 작은 경우 Flip이 되지 않아 Read 동작에 안정성 문제를 해결할 수 있습니다.

| "1" WRITE | "0" WRITE |

| ① WL에 VDD(≥ VTH) 인가 → 2개의 Transistor(Switch) turn-on ② WBL = VDD (WBLB = 0) → Inverter(M4, M6) = 0 ③ QB = 0 |

① WL에 VDD(≥ VTH) 인가 → 2개의 Transistor(Switch) turn-on ② WBL = 0 (WBLB = VDD) → Inverter(M4, M6) = VDD ③ QB = 1 |

Inverter chain state를 QB의 Charging(1)/Discharging(0)으로 Data(1/0)을 저장합니다.

| "1" READ | "0" READ |

| ① WL에 VDD(≥ VTH) 인가 → 2개의 Transistor(Switch) turn-on ② RWL에 VDD(≥ VTH) 인가 → M8 Turn-on ③ QB = 0 → M7 Turn-on ④ RBL capacitance charging |

① WL에 VDD(≥ VTH) 인가 → 2개의 Transistor(Switch) turn-on ② RWL에 VDD(≥ VTH) 인가 → M8 Turn-on ③ QB = 1 → M7 Turn-off ④ RBL capacitance discharging |

|

|

8T SRAM은 2개의 추가된 Transistor를 통해서 독립적인 Read-port으로 운용할 수 있기 때문에 QB의 전하에 의해 M7 작동 여부를 결정하기 때문에 Non-destructive read 방식입니다. 또한, 2개의 추가된 Transistor가 추가적인 Leakage current path으로 작용하기 때문에 Standard 6T SRAM에 비해 Leakage current가 높습니다.

♭ 10T SRAM

10T SRAM은 8T SRAM에 추가된 Transistor에 의해 발생하는 Leakage currrent 개선하기 위하여 독립적인 Read-port에 2개의 Transistor(CMOS)를 더 추가한 구조입니다. 2개의 추가적인 Transistor를 통해 Un-accessed bit cell으로 발생하는 Leakage current를 제어할 수 있습니다.

| "1" WRITE | "0" WRITE |

| ① WL에 VDD(≥ VTH) 인가 → 2개의 Transistor(Switch) turn-on ② WBL = VDD (WBLB = 0) → Inverter(M4, M6) = 0 ③ QB = 0 |

① WL에 VDD(≥ VTH) 인가 → 2개의 Transistor(Switch) turn-on ② WBL = 0 (WBLB = VDD) → Inverter(M4, M6) = VDD ③ QB = 1 |

8T SRAM과 마찬가지로 Inverter chain state를 QB의 Charging(1)/Discharging(0)으로 Data(1/0)을 저장합니다.

| "1" READ | "0" READ |

| ① WL에 VDD(≥ VTH) 인가 → 2개의 Transistor(Switch) turn-on ② RWL에 VDD(≥ VTH) 인가 → M8 Turn-on ③ QB = 0 → 추가한 CMOS의 PMOS Turn-on ④ RBL capacitance discharging |

① WL에 VDD(≥ VTH) 인가 → 2개의 Transistor(Switch) turn-on ② RWL에 VDD(≥ VTH) 인가 → M8 Turn-on ③ QB = 0 → 추가한 CMOS의 NMOS Turn-on ④ RBL capacitance discharging |

|

|

<출처>

"Memory", ICE(Integrated Circuit Engineering Co. Ltd), (1997).

D. Tripathy et al. "A single-ended TG based 8T SRAM cell with increased data stability and less delay" , IEEE, (2017).

N. Devarajan, V. Rukkumani, "Design and analysis of static random access memory by schmitt trigger topology for low voltage applications", J. Eng. Sci. Tech., 11 (2016) 1722-1735.

오류가 있다면 지적해주시면 감사하겠습니다 :)

'반도체소자' 카테고리의 다른 글

| [반도체소자] 22. NAND (2) (2) | 2024.01.25 |

|---|---|

| [반도체소자] 21. NAND (1) (2) | 2024.01.23 |

| [반도체소자] 19. 1T DRAM (Capacitor-less DRAM) (0) | 2023.07.24 |

| [반도체소자] 18. DRAM (3) (0) | 2023.07.21 |

| [반도체소자] 17. DRAM (2) (0) | 2023.07.21 |