| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | ||||||

| 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| 16 | 17 | 18 | 19 | 20 | 21 | 22 |

| 23 | 24 | 25 | 26 | 27 | 28 |

- Threshold Voltage

- MOSFET

- 반도체공학

- effective mass

- Silicon on Insulator

- ion implantation

- 반도체소자

- She

- 양자역학

- 선결함

- RCAT

- Punch through

- mechanism

- DRAM

- SOI MOSFET

- 부피결함

- high bandwidth memory

- oxidation

- Energy Band

- 반도체 8대공정

- finFET

- SK하이닉스

- doping

- Dynamic Random Access Memory

- HBM

- feol

- Warpage

- GIDL

- 반도체공정

- Short Channel Effect

- Today

- Total

반도체 공부 기록

[반도체소자] 22. NAND (2) 본문

NAND

Flash memory 성능은 같은 면적 대비 큰 용량을 저장할 수 있을 수록 좋습니다.

NOR Flash 특징

1. 바이트나 워드 단위로 읽기/쓰기가 가능하고 덮어쓰기와 지우기는 임의로 접근할 수 없다.

2. 읽기 속도는 Access 속도가 빠르나, 쓰기/지우기 속도는 느리다.

NAND Flash 특징

1. 페이지 단위로 읽기/쓰기가 가능하고 해당 페이지를 지우거나 덮어쓰기를 하려면 모든 블럭을 지워야 한다.

2. 크기가 작고 단가가 저렴하고, 대용량 저장이 가능하다.

3. NOR Flash와 반대로 데이터를 읽을 때 Access 속도가 느리지만, 쓰기/지우기 속도는 빠르다.

♭ Multi-cell NAND

| SLS(Single Level Cell) | MUL(Multi Level Cell) |

| 메모리 셀 하나에 1bit를 저장하는 기술 | 메모리 셀 하나에 2bit를 저장하는 기술 |

| TLC(Triple Level Cell) | QLC(Quadraple Level Cell) |

| 메모리 셀 하나에 3bit를 저장하는 기술 | 메모리 셀 하나에 4bit를 저장하는 기술 |

| |

NAND Flash의 메모리 용량을 늘리기 위해 메모리 Cell당 저장할 수 있는 데이터의 양(Bit)을 늘립니다.

메모리 Cell에 저장하는 데이터 양이 작을수록 읽기/쓰기 속도는 빠르지만, 가격이 비싸다는 단점이 있습니다.

반대로 메모리 Cell에 저장하는 데이터 양이 많을수록 읽기/쓰기 속도는 느리지만, 가격이 저렴하다는 장점이 있습니다.

| SLC | MLC | TLC | |

| Level cell | 1bit/cell | 2bit/cell | 3bit/cell |

| Eudurance cycle(P/E) | 50,000 ~ 100,00회 | 3,000 ~ 10,000회 | 500 ~ 1,000회 |

| Read time | 25㎲ | 50㎲ | ~75㎲ |

| Write time | 200 ~ 300㎲ | 600 ~ 900㎲ | ~900 ~ 1350㎲ |

| Erase time | 1.5 ~ 2㎳ | 3㎳ | ~4.5㎳ |

| Cost | Very High | Medium | Medium Low |

♭ Read operation (String)

String sturcture = 2개의 Select transistor(SGS, SGD) + n개의 Cell

String 구조를 갖는 NAND Flash memory는 다수의 cell들(8 cells → 16 cells → 32 cells → 64 cell...)이 존재한다. 각각의 Cell마다 Program/Erase operation에 의해 Floating gate에 존재하는 전자(전하)의 수가 상이하여 산포를 갖는다. 산포가 좁을수록(적색) 유리하며, 산포가 넓으면(청색) Program state와 Erase state를 구분할 수 없다.

*SGS: Source side selected gate, SGD: Source side selected gate - Bit line 스위치 역할

가령, 우리가 읽고자 하는 Cell(Selected cell)이 W3(Word line #3)에 연결되어 있다고 가정해보자. Unselected cell(읽지 않는 Cell)의 Word line에 전압이 인가되어 있지 않으면 String 단위로 묶여 있기 때문에 W3 cell에 Bit line에 인가된 전압이 흐르지 않아 데이터를 읽을 수 없다. 읽지 않는 Cell이 전압이 연결되지 않으면 읽고자 하는 Cell에 Bit line의 전압이 전달되지 않기 때문에 읽기 동작을 수행할 수 없어 Unselected cell에는 Vpass 인가하여 Turn-on 시킨다.

1. SGS, SGD에 VDD를 인가하여 Turn-on: String 연결

2. Selected cell에는 Vread 인가, Unselected cell에서 Vpass 인가

-Selected cell(W3에 연결된 Cell)

Selected cell은 Program/Erase state에 따라 Icell 결정

1) Program state: Floating gate or Charge trap layer에 전자가 존재하는 경우 - Threshold voltage positive shift

WL3에 Vread 인가 시 Icell = 0

2) Erase state: Floating gate or Charge trap layer에 전자가 존재하지 않은 경우 - Threshold voltage negative shift

WL3에 Vread 인가 시 Icell > 0

-Unselected cell(W3을 제외한 Cell)

Unselected cell의 Program/Erase state에 상관없이 Turn-on: Bit line의 전압을 W3 cell에 전달하기 위한 목적

전압 크기: VTH(E) < Vread < VTH(P) < Vpass

-Pass disturb

Selected String에서 Read 동작을 위해 Unselected cell들에 Vpass에 인가할 때 FN Tunneling이 일부 발생하여 Selected cell 주위의 Unselected cell들이 Soft program이 발생하는 Pass disturb 현상이 일어난다.

♭ Flash memory program/erase operation

*IPD: Inter-poly oxide

Flash memory은 Tunneling을 통해 Tunneling oxide에 전자(전하)가 존재하면 Program, 전자가 존재하지 않은면 Erase가 됩니다. Flash memory의 Program/Erase operation은 Tunneling에 의해 이루어지고, Tunneling mechanism 2가지를 알아보도록 하겠습니다.

1. Fowler-Nordheim Tunneling (FN tunneling)

Gate와 Substrate(or Source)에 전압을 인가하여 Tunneing oxide의 에너지 장벽(삼각형 밑변의 길이)만큼 Tunneling

-Tunneling oxide: FN tunneling이 발생해야 하므로 얇은 두께를 갖는 Tunneing oxide가 요구 → Program/Erase operation voltage는 Tunneling oxide의 두께(Tunneling width)에 의존

-IPD: Control gate로 전자가 Back tunneling 되는 것을 방지하는 Block oxide 역할 → Back tunneling을 방지하기 위해 두꺼운 두께의 IPD 요구

1) NAND Program/Erase, NOR Erase operation mechanism

2) Drain에 전압을 인가하지 않아도 FN tunneling 발생

3) 별도의 Charge pumping circuit 요구

4) P/E Low speed, High efficiency: 전하 100개 중 99% Tunneling 참여 (숫자는 HCI와 비교하기 위한 상대적인 값)

2. Hot carrier injection (HCI)

Saturation(VFG > VTH, VDS ≥ VFG - VTH) 동작 영역에서 Drain에 인적한 영역에서 Hot carrier가 Tunneling oxide의 Barrier를 극복하는 Tunneling

1) NOR Progam operation mechanism

2) Drain에 전압 요구: 강한 전기장에 의한 전하 가속 (Hot carrier 전제 조건)

3) Only available program: Hot carrier는 전기장에 의해 가속된 전하를 의미하는데, Floating gate에서 전자를 가속시킬 수 없기 때문에 HCI로 Erase operation 수행이 불가능

4) P/E High speed, Low efficiency: 전하 100만개 중 1%가 Tunneling 참여

https://mse-semi.tistory.com/10

[반도체소자] 8. Hot Carrier Injection(HCI)

Hot Carrier Injection(HCI) Hot Carrier Injcection(HCI)는 GIDL과는 다르게 Drain depletion 영역의 강한 전기장에 의해 Leak current(Gate cuurent)가 발생하는 Short Channel Effect(SHE)입니다. (HCI는 Long channel MOSFET에서도 발생

mse-semi.tistory.com

-IPD의 Capacitance는 크고, Tunneling oxide의 Capacitance은 작을수록 Control 효율이 높다. → Control gate에 인가하는 Vpgm이 작아도 Program이 가능하다.

Q) IPD의 Capatitance는 크고, Tunneling oxide의 Capcitance는 작아야 하는 이유?

A) Capacitive coupling

Hot carrier injcetion이 발생하는 곳은 Tunneling oxide로 Floating gate와 Channel 사이의 전압 차이에 결정되기 때문이다.

Flash memory를 모델링하면 위 그림과 같다. 가령, IPD의 Capacitance가 8pF, Tunneling oxide의 Capacitance가 4pF, Control gate에 12V가 인가된다고 가정해보자. Capacitor의 직렬 연결로 Charge는 일정하고, Total capcitance는 다음과 같이 정의된다. Capacitive coupling에 의해 Control gate에 인가된 전압이 그대로 Floating gate에 전달되지 않는다. Hot carrier injcetion에 의해 발생하는 Tunneling은 Floating gate와 Channel 사이의 전위차에 결정되기 때문에 Vtunn은 다음과 같이 정의된다. Vtunn 수식에 따라 IPD의 Capacitance 값이 클수록 Control gate에 인가되는 전압이 작아도 Floating gate에 전달되는 전압이 크기 때문에 Program operation이 가능하다.

Q) NAND flash memory에서Program/Erase operation에서 FN tunneling을 사용하는 이유?

A) NAND flash memory는 고집적화를 위해 String에 Cell의 수가 늘고 있으며, String 구조는 하나의 Bit line이 2개 이상의 Cell를 제어한다. 하나의 Bit line의 각 Cell에 대해 독립적인 Bias 인가가 어렵기 때문에 강한 전기장에 의한 전자(전하)의 가속이 어렵기 때문에 HCI에 의한 Tunneling 방식으로 P/E operation이 불가능하다. (Vpass를 인가하여 Floating gate에 전압을 전달해도, Channel의 저항이 크기 때문에 Drain current를 크게하는 것이 어려워 HCI mechanism이 불가능하다.)

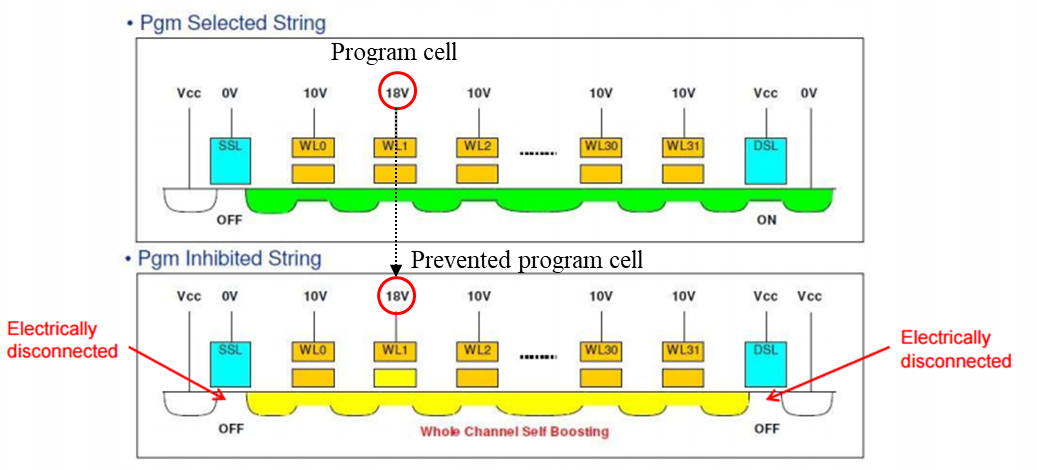

♭ Program operation (String) : Self-boosting

Self-boosting은 Selected string에서 Selected Cell의 WL을 공유하는 Unselected string의 Unselected cell의 Program을 방지하는 기술이다.

1. Selected string, Unselected string 모두 SSL(Seleted Source Line)의 Transistor gate에 0V를 인가하여 Turn-off시켜 VCC가 인가된 Source line가 끊어준다.

2. Selected String에서 Selected cell에 Program 하기 위해 Vpgm = 18V (WL1)을 인가

(cf: Selected string에서 Unselected cell에는 Vpass = 10V 인가 → Pass disturb 발생)

3. Unselectrd string에서의 Selected string의 Selected cell의 Word line(WL1)과 연결된 Cell에 Program 방지가 필요하다.

3-1. Unseleted string의 Bit line에 VCC(VBoost) 인가

→ VCC 인가 시 Unselected string의 Cell channel 전제가 VCC - VTH 까지 전압 증가

(cf: DSL의 Transistor로는 제어가 불가능하다: DSL Tr. turn-off 시 Selected string에서 Program 불가)

3-2. Unselected string의 Unselected cell(WL1에 연결되어 있지 않은 모든 Cell)에 Vpass 인가

→ Vpass 인가 시 Channel은 Vpass와 Capacitive coupling에 의한 전압 증가(Boosting) : Vpass × C.C.R.Sub.

(*C.C.RSub.: Substrate의 Capacitive coupling ratio)

3-3. Unselected string의 Selected cell(WL1에 연결된 Cell)에 Vpgm 인가

→ Vpga 인가 시 Channel은 Vpgm과 Capacitive coupling에 의한 전압 증가(Boosting) : Vpgm × C.C.R.Sub.

3-4. Self-boosting에 의해 Floating gate와 Channel 사이의 Potential (VFG-VSub.) 차이 감소

→ Potential 차이가 감소하므로, 전자(전하)가 FN tunneling을 하지 못하여 Program을 방지한다.

VSub. = VCC - VTH + Vpass × C.C.R.Sub. + Vpgm × C.C.R.Sub.까지 Boosting하여 Potential 차이에 의해 Tunneling을 방지한다.

<출처>

S. Lee, J. Kim, "Improving Performance anc Capacity of Flash Storge Devices by Exploiting Heterogeneity of MLC Flash Memory", IEEE Transactions on Computer, 63 (2013) 2445-2458.

오류가 있다면 지적해주시면 감사하겠습니다 :)

'반도체소자' 카테고리의 다른 글

| [반도체소자] 21. NAND (1) (2) | 2024.01.23 |

|---|---|

| [반도체소자] 20. SRAM (0) | 2023.07.26 |

| [반도체소자] 19. 1T DRAM (Capacitor-less DRAM) (0) | 2023.07.24 |

| [반도체소자] 18. DRAM (3) (0) | 2023.07.21 |

| [반도체소자] 17. DRAM (2) (0) | 2023.07.21 |