| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | ||||||

| 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| 16 | 17 | 18 | 19 | 20 | 21 | 22 |

| 23 | 24 | 25 | 26 | 27 | 28 |

- She

- SOI MOSFET

- effective mass

- Punch through

- Dynamic Random Access Memory

- doping

- high bandwidth memory

- SK하이닉스

- 반도체공학

- Energy Band

- Silicon on Insulator

- finFET

- 반도체소자

- Warpage

- Short Channel Effect

- 반도체공정

- Threshold Voltage

- DRAM

- 양자역학

- 반도체 8대공정

- 부피결함

- mechanism

- RCAT

- GIDL

- feol

- oxidation

- ion implantation

- HBM

- MOSFET

- 선결함

- Today

- Total

반도체 공부 기록

[반도체소자] 18. DRAM (3) 본문

DRAM(Dynamic Random Access Memory)

DRAM의 정보를 보존하기 위해서는 Refresh 동작이 반드시 필요하지만, Refresh 동작은 지속적으로 전력 소모를 초래합니다. 따라서 Refresh 특성을 개선하는 방안에 대해서 알아보도록 하겠습니다. 이전 포스팅에서도 간략하게 언급했지만, Leakage current를 제어하거나 Cell capacitance를 증가시켜 Refresh 특성을 개선할 수 있습니다. Leakage current를 개선하는 경우는 Cell capacitor에서 빠져나가는 전하의 수를 줄일 수 있고, Cell capacitance를 증가시키면 Cell에 저장할 수 있는 전하의 수가 늘어나 Refresh 특성을 개선할 수 있습니다. 전하가 똑같이 모종의 이유로 10개가 손실되는 DRAM에서 Cell capacitor의 저장 능력(Cell capacitance)가 20개에서 200개로 증가하는 경우 전하의 손실에도 정보("0" 또는 "1")가 보존될 수 있기 때문입니다.

♭ Leakage current control

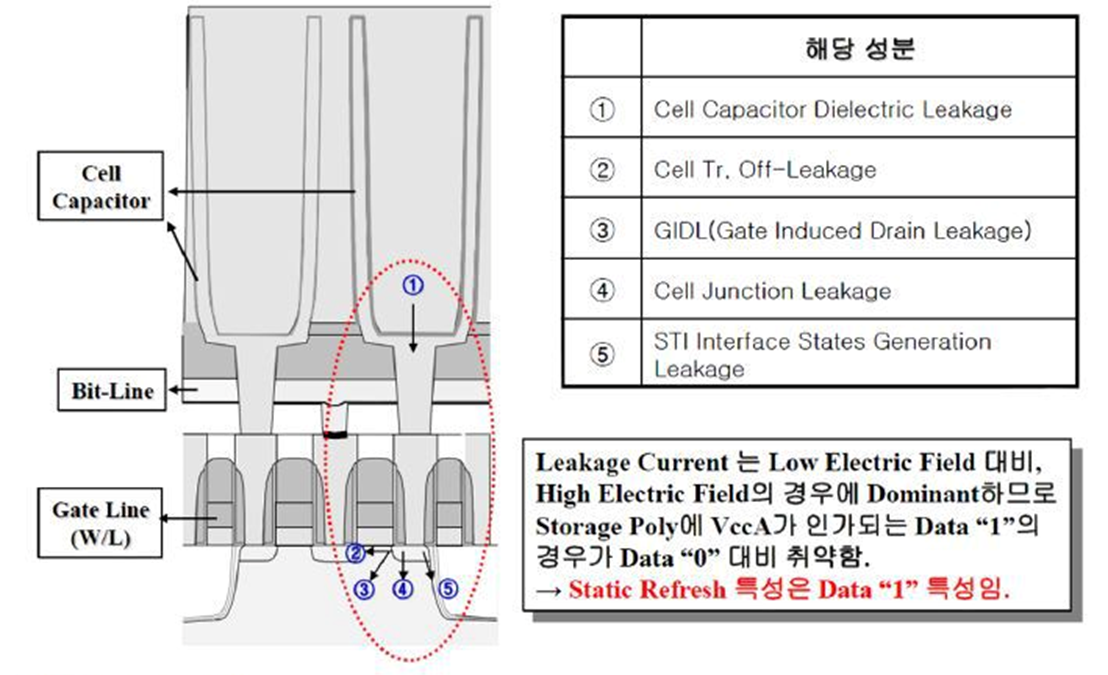

DRAM에서는 앞에서 언급한 두 가지 Leakage current 이외에도 GIDL, Cell capacitor dielectric leakage current, STI interface states generation leakage current 등 다양한 누설 전류가 존재합니다. DRAM 내부에서 발생하는 누설 전류(Short channel effect)를 제어하는 경우 손실되는 전하를 줄여 Refresh 특성을 개선할 수 있습니다.

1. RCAT(Recess cell array transistor)

RCAT 기술을 이용하여 Effective channel length를 증가시켜 Short channel effect를 개선하여 Retention time를 증가시킬 수 있습니다. Retention time의 증가로 Refresh 주기가 길어질 수 있고 이에 따라 DRAM에서 소모되는 전력의 크기가 감소합니다.

https://mse-semi.tistory.com/16

[반도체소자] 13. Advanced MOSFET

Advanced MOSFET소자 미세화에 따라 발생하는 SHE(Short channel effect)를 제어하기 위해서 SOI MOSFET과 같은 다양한 기술이 개발되었습니다. 이번 포스팅에서는 SHE를 효과적으로 제어하기 위한 다양한 기술

mse-semi.tistory.com

2. Saddle MOSFET (RCAT + FinFET)

Saddle MOSFET은 RCAT과 FinFET 기술을 접목시킨 기술입니다. RCAT 기술을 사용하는 경우 Effective channel lenngth는 증가하여 Short channel effect를 제어하여 누설전류를 줄일 수 있습니다. 하지만 RCAT의 경우 Electron path가 증가하여 낮은 On-current를 가지는 한계점을 가지고 있습니다. 이를 극복하기 위해서 RCAT 기술에 FinFET 구조를 접목하여 낮은 On-current 특성을 개선할 수 있습니다.

Saddle MOSFET은 RACT에 비해 높은 Ion/Ioff 특성을 가지고 있습니다. RCAT의 경우 Etch depth에 따라 Threshold voltage modulation이 발생하여 소자 설계에 어려움이 있지만, Saddle MOSFET의 경우 Etch depth에 따라 Threshold voltage가 비교적 일정하기 때문에 설계에 용이합니다. (RCAT은 Etch depth에 따라 Body effect의 영향을 민감하게 받기 때문에 Threshold voltage modulation 현상이 발생합니다.)

♭ Cell capacitance

Cell capacitance(C = ε×A/d)를 증가시키기 위해서는 여러가지 방법(1. 유전상수 증가, 2. 면적 증가, 3. 거리 감소)이 있습니다. 하지만 소자 미세화에 따라서 Cell capacitance를 증가시키기 위해서 Capacitor의 면적(XY평면; 기판과 평행한 면)을 증가시키는 것은 어려움이 있습니다.

1. High aspect ratio capacitor

소자 미세화에 따라서 Capacitor의 면적을 쉽게 늘리지 못하여 Cell capacitance를 증가시키기 위해서 Capacitor를 3차원 구조를 통해 면적을 증가시켰습니다. 높은 종횡비를 가지는 Capacitor 구조를 이용하여 넓은 면적을 얻을 수 있었습니다. 하지만 각각의 방식에 따라 문제가 있습니다.

-Trench DRAM

1. Capacitance 증가에 따라서 더 깊은 Trench가 요구되는데 Trench를 형성하기 위하여 High aspect ration silicon etch(HARSE)가 요구됩니다. 하지만 깊은 Trench를 형성하는 과정에서 깊이가 일정하지 않아 Cell capacitance 값이 일정하지 않은 한계가 있습니다.

2. DRAM을 동작하기 위하여 Selected transistor를 만드는 공정에서 Capacitor에 문제가 발생합니다. Seleceted Tr.을 형성하기 위해서는 Source/Drain을 형성하기 위해 IMP(Ion implantation) 이후 Activation 과정과 같이 고온이 필요한 공정이 있습니다.

-Stack DRAM

Trench DRAM에서의 단점 때문에 현재 DRAM은 모두 Stack capacitor를 적용하고 있습니다. 하지만 Stack DRAM에도 문제가 발생하는데, DRAM의 발전에 따라 더 높은 Cell capacitance 값이 요구됨에 따라 더 높은 Aspect ratio를 가지는 Stack Capacitor가 요구됩니다. 이에 따라 Capacitor가 안정적으로 서있지 못하고 쓰러지게 되어 다른 구조물과 접촉하여 전기적 단락(Short)를 발생시킵니다. 현재 이를 해결하기 위해서 Capacitor가 안정적으로 유지할 수 있도록 지지대를 추가로 만들어줍니다.

2. High-K dielectric material

DRAM 발전에 따라 높은 Cell capacitance가 요구되어 3D 형태의 Capacitor를 이용하여 면적을 늘렸습니다. 하지만 기계적 구조에 의한 한계나 공정 난이도의 문제로 Cell capacitor에 높은 유전 상수를 가지는 High-K 물질을 적용하기도 합니다. 하지만 High-K의 경우 낮은 Conduction band offset으로 전하가 에너지 장벽을 쉽게 넘어 손실되는 한계가 있습니다.

https://mse-semi.tistory.com/13

[반도체소자] 10. Gate leakage current

Gate leakge current 반도체 소자는 Moore's law에 따라 소자의 크기가 작아지고, 집적도는 향상되었습니다. 소자 미세화에 따라 Channel length가 짧아져서 Short channel effect가 발생하여 소자의 performance를 감

mse-semi.tistory.com

DRAM에서는 전하가 손실되는 것은 사용자가 저장한 정보가 사라지기는 것이기 때문에 절대적으로 예방해야 하는 상황입니다. 그래서 DRAM에서는 High-K 물질을 하나만 이용하는 것이 아니라 여러 물질을 복합적으로 사용하여 High-K의 단점인 낮은 Conduction band offset를 극복하고자 합니다. 대표적인 사례로 ZAZ(ZrO2/Al2O3/ZrO2) 구조가 있습니다. ZAZ 구조는 높은 유전상수를 가지는 ZrO2 사이에 넓은 밴드갭(높은 Conduction band offset)을 가지는 Al2O3를 삽입하는 구조를 사용합니다. ZrO2를 이용하여 Cell capacitance를 증가시키고, Al2O3를 이용하여 ZrO2의 낮은 Conduction band offset으로 손실되는 전하를 방지합니다.

<출처>

D. Y. Choi, "Industry Report - Semiconductor", Kyobo Securities Co., Ltd, (2016).

Y. K. Kim et al., "Partial Isolation Type Saddle-FinFET(Pi-FinFET) for Sub-30 nm DRAM Cell Transistors", Electronics, 8 (2018) 8.

K. H. Park et al., "Highly Scalable Saddle MOSFET for High-Density and High-Performance DRAM", IEEE, 26 (2005) 690-692.

H. W. Chung et al., "Novel 4F2 DRAM cell with Vertical Pillar Transistor(VPT)", ESSDERC, (2011) 211-214.

오류가 있다면 지적해주시면 감사하겠습니다 :)

'반도체소자' 카테고리의 다른 글

| [반도체소자] 20. SRAM (0) | 2023.07.26 |

|---|---|

| [반도체소자] 19. 1T DRAM (Capacitor-less DRAM) (0) | 2023.07.24 |

| [반도체소자] 17. DRAM (2) (0) | 2023.07.21 |

| [반도체소자] 16. DRAM (1) (0) | 2023.07.19 |

| [반도체소자] 15. FinFET (2) (0) | 2023.07.13 |