| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | ||||||

| 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| 16 | 17 | 18 | 19 | 20 | 21 | 22 |

| 23 | 24 | 25 | 26 | 27 | 28 |

- 반도체공정

- GIDL

- SK하이닉스

- high bandwidth memory

- Energy Band

- Punch through

- 양자역학

- She

- 반도체소자

- oxidation

- mechanism

- Dynamic Random Access Memory

- doping

- 선결함

- effective mass

- SOI MOSFET

- 부피결함

- DRAM

- Short Channel Effect

- 반도체 8대공정

- finFET

- ion implantation

- Threshold Voltage

- RCAT

- HBM

- MOSFET

- feol

- Warpage

- Silicon on Insulator

- 반도체공학

- Today

- Total

반도체 공부 기록

[반도체소자] 16. DRAM (1) 본문

DRAM(Dynamic Random Access Memory)

DRAM은 1개의 Selected Transistor와 1개의 Capacitor(1T1C)를 가지는 메모리 소자로 RAM(Random Access Memory)의 한 종류입니다. DRAM은 1T1C의 구조로 정보(Data)를 Capacitor에 저장을 하고 Transistor의 스위치 동작에 따라 정보를 쓰고(Write), 읽습니다(Read).

메모리는 정보에 접근하는 방식이 Sequential access와 Random access 2가지 방식이 있습니다. 먼저 Sequential access은 과거의 카세트 테이프에 사용되었고, Random access는 현재 스마트폰, PC 등에 사용되고 있습니다. 두 방식 차이에 대해서 알아보도록 하겠습니다. 1~10번의 노래가 있다고 가정하겠습니다. 사용자가 4번 노래를 듣고 싶은 경우 Random access 방식을 사용하는 현재는 4번 노래를 재생시키면 되지만, 과거 Sequential access 방식을 사용하는 경우에는 1~3번 노래를 모두 지나치고 4번 노래를 재생할 수 있었습니다.

♭ Data 저장 장소, 저장하는 물리량

Charge를 Capacitor에 저장하여 Capacitor의 Charge 유무로 Data(0/1)을 구분합니다.

♭ Write 방식

| '1' WRITE | '0' WRITE |

| ① WL에 VDD(≥VTH) 인가 → Selected Tr. Turn-on ② BL에 VDD 인가 ③ Cell capacitor charging |

① WL에 VDD(≥VTH) 인가 → Selected Tr. Turn-on ② BL에 0V 인가 ③ Cell capacitor discharging |

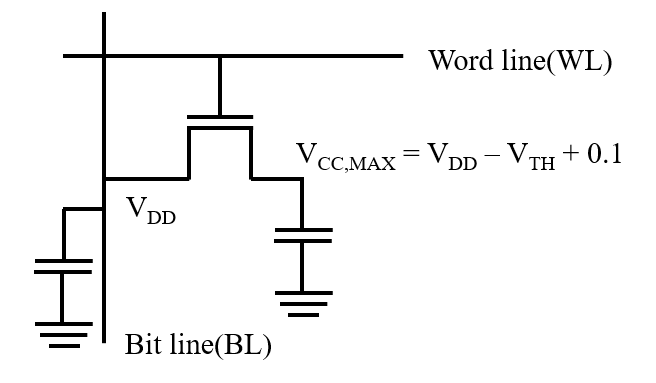

'1' Writing 시 VCC(Cell capacitor voltage)의 최댓값은 VCC,MAX = VDD-VTH입니다. 만약 VCC,MAX > VDD-VTH이 되면 Selected transistor에 인가되는 경우를 가정하면, 수직 방향의 전기장 성분이 Threshold voltage보다 작아져 Selected Tr.이 Turn-off가 됩니다.

예를 들어 VCC,MAX = VDD - VTH + 0.1 (>VDD - VTH) 인가되는 경우 Selected Tr. 사이의 전압차는 VDD - VCC,MAX (VDD - VTH + 0.1)으로 VTH - 0.1의 값으로 Selected Tr.에 인가된다. 따라서 VTH - 0.1 < VTH 이므로 Turn-off 되어 전하를 저장할 수 없습니다. 따라서 Cell capacitor에 저장할 수 있는 전하의 양은 VDD - VTH으로 제한됩니다.

♭ Read 방식

| '1' READ | '0' READ |

| ① BL에 Low voltage 인가 → BL capacitor 상태 초기화 ② WL에 VDD(≥VTH) 인가 → Selected Tr. Turn-on ③ VCC 감소 (Discharging) → VB 증가 : Charge sharing ④ Sense amplifier로 ΔVB 증폭 |

① BL에 Low voltage 인가 → BL capacitor 상태 초기화 ② WL에 VDD(≥VTH) 인가 → Selected Tr. Turn-on ③ VCC 증가 (Charging) → VB 증가 : Charge sharing ④ Sense amplifier로 ΔVB 증폭 |

Cell capacitor에 '1'이 저장되어 있는 경우 Cell capacitor의 초기 상태는 QCC = CCC(VDD - VTH)으로 충전되어 있습니다. 정보(Data)를 읽기 위해서 BL에 낮은 전압을 인가하여 CB를 Pre-charge 시켜 상태를 초기화 시킵니다. (Pre-charge 과정은 Read 동작을 하기 전에 이전의 수행된 동작에 의한 BL capacitor의 상태를 초기화시켜 Read 동작을 준비합니다.) 이후 Selected Tr.에 전압을 인가하여 Tunr-on 시키면 Cell capacitor의 전하가 BL capacitor로 이동합니다. DRAM은 이 일련의 과정을 통해서 BL의 전하 변화에 의해 발생하는 전압(전류) 변화량을 통해서 정보(Data)를 읽습니다.

BL capacitance가 Cell capacitance에 비해 일반적으로 매우 큰 값을 가지기 때문에 ΔVB(~60mV)가 매우 작은 값을 가지기 때문에 Sense amplifier를 통해서 ΔVB 값을 증폭시켜 정보(Data)를 읽습니다. DRAM의 경우는 Charge의 이동에 의해 정보(Data)를 읽기 때문에 한 번 읽게 되면 또 다시 읽을 수 없는 Destructive read 방식을 가지고 있습니다.

<출처>

S. K. Kim et al., "Capacitors with an Equivalent Oxide Thickness of <0.5nm for Nanoscale Electronic Semiconductor Memory", Adv. Funct. Mater., 20 (2010) 2989-3003.

오류가 있다면 지적해주시면 감사하겠습니다 :)

'반도체소자' 카테고리의 다른 글

| [반도체소자] 18. DRAM (3) (0) | 2023.07.21 |

|---|---|

| [반도체소자] 17. DRAM (2) (0) | 2023.07.21 |

| [반도체소자] 15. FinFET (2) (0) | 2023.07.13 |

| [반도체소자] 14. FinFET (1) (0) | 2023.07.11 |

| [반도체소자] 13. Advanced MOSFET (0) | 2023.07.05 |