| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | ||||||

| 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| 16 | 17 | 18 | 19 | 20 | 21 | 22 |

| 23 | 24 | 25 | 26 | 27 | 28 |

- Threshold Voltage

- Warpage

- Silicon on Insulator

- 부피결함

- GIDL

- Dynamic Random Access Memory

- effective mass

- finFET

- 반도체 8대공정

- 반도체공학

- feol

- Short Channel Effect

- 반도체소자

- 양자역학

- mechanism

- Punch through

- DRAM

- 반도체공정

- high bandwidth memory

- 선결함

- SK하이닉스

- oxidation

- ion implantation

- SOI MOSFET

- RCAT

- MOSFET

- She

- Energy Band

- HBM

- doping

- Today

- Total

반도체 공부 기록

[반도체소자] 15. FinFET (2) 본문

FinFET

SCE를 개선하기 위해 Channel을 3면을 통해 제어하는 FinFET이 개발되었습니다. 하지만 FinFET에서 여전히 구조적/공정적인 이슈 때문에 문제가 남아있습니다. 이번 포스팅에서는 FinFET에서 발생하는 이슈에 대해서 알아보도록 하겠습니다.

♭ Corner effect

FinFET의 Fin 모서리(Corner) 부분에 전기장이 집중되어 Threshold voltage 이하의 전압 영역에서 국부적으로 Turn-on이 발생하는 현상입니다. Corner effcet에 의한 국부적인 Turn-on은 Transfer curve에서 hump으로 나타납니다. Corner effect가 발생하는 경우 hump에 의한 영향으로 SS이 증가합니다. Corner effect를 해결하기 위해서 Fin 상부에 두꺼운 산화막을 형성하였고, 이후 둥근 Fin 형태로 발전하다가 최종적으로는 균일한 전기장 분포를 형성하기 위해 GAAFET이 개발되었습니다.

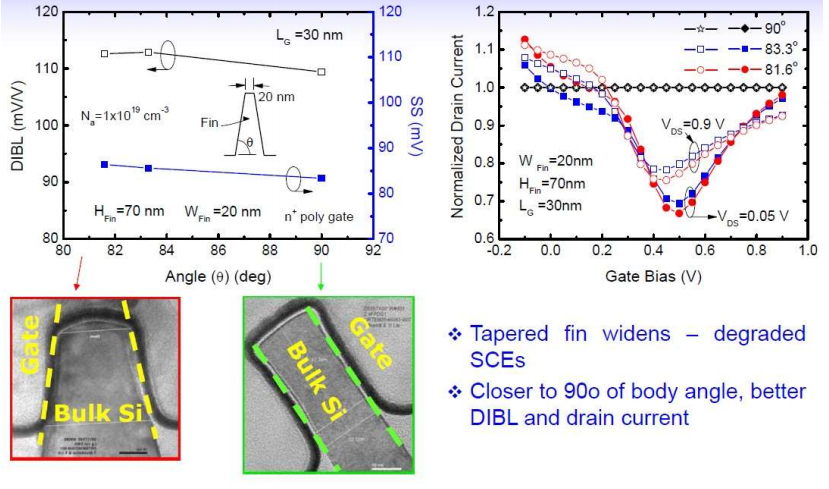

♭ Body angle(Fin profile)

FinFET은 Anisotropic profile을 가지는 Fin의 구조를 가지는 것이 매우 중요합니다. Anisotropic fin profile을 위해서는 Anisotropic etch 공정이 필요합니다. Fin의 Aspect ratio가 낮은 경우 Effective channel length의 감소로 (2Hfin + Wfin에서 Hfin이 감소) On-current의 크기가 감소합니다. 따라서 On-current를 증가시키기 위해서 Hfin을 증가시키게 되는데, 이에 따라 공정 난이도(Anisotropic etch)가 증가하여 Body angle이 증가하게 됩니다. Body angle 증가에 따라 FinFET Design시 설정한 Wfin보다 넓은 Wfin을 가지는 영역(Fin의 하부 영역)에 대해서는 Gate controllability가 국부적으로 감소하게 됩니다. 이에 따라 Gate controllability가 낮은 영역에서는 SCE가 발생하여 FinFET의 Performance를 낮추게 됩니다.

♭ Back bias effect

Back bias에 의해 FinFET의 Threshold voltage modulation이 발생하고, SS 특성이 악화되는 것을 확인할 수 있습니다. Back bias effect는 FinFET의 Fin width와 상관관계가 있습니다. Fin이 두꺼울수록 Gate controllability가 감소하기 때문에 Back bias에 의한 영향을 받지만, Fin이 얇을수록 Gate controllability가 증가하여 Back bias에 의한 영향을 받지 않습니다(Floating body). 따라서 Fin width가 증가할수록 수평방향의 전기장 성분이 Fin에 의해 영향을 미치기 때문에 Back bias effect에 의한 영향을 많이 받아 SS가 증가합니다.

♭ Source/Drain junction(Punch through)

Bulk FinFET을 사용하는 경우 Source와 Drain의 Depletion layer가 만나 Leakage current를 만들게 됩니다.

→ Low body doping, Source/Drain juction depth > Fin height

Low body doping은 Source/Drain의 Depletion layer의 두께가 증가하고, Junction depth가 Fin height에 보다 큰 경우는 Bulk 영역에서 Punch through가 발생하여 FinFET의 성능을 감소시킵니다. (DIBL 증가, SS 증가)

Punch through를 개선하기 위해서는 국부적으로 Heavy doping(PTS; Punch through stopper)을 통해 방지할 수 있습니다. Punch through의 원인으로 지적되었던 Low body doping을 해결하기 위해서 Body doping 농도를 증가시키는 경우 FinFET design 시 설정한 Threshold voltage와 다른 전압 조건에서 FinFET이 Turn-on 되기 때문에 Body doping 농도는 쉽게 증가시킬 수 없습니다.

<출처>

T. J. K. Liu, "FinFET History, Fundamentals and Future", Symp. VLSI Tech., (2012).

A. N. Moulai Khatir et al., "SOI-Multi-FinFET: Impact on Fins Number multiplicity on Corner Effect", NSTS-Nanotech., 2 (2014) 411-415.

"Silicon nanoeletroincs workshop", IEEE, (2003).

J. Biswas et al., "Impact on Punch-through Stop Implants on Channel Doping and Junction Leakage for Ge p-FinFET Applications", IEEE Transactions on Electron Devices, 66 (2019) 1635-1641.

오류가 있다면 지적해주시면 감사하겠습니다 :)

'반도체소자' 카테고리의 다른 글

| [반도체소자] 17. DRAM (2) (0) | 2023.07.21 |

|---|---|

| [반도체소자] 16. DRAM (1) (0) | 2023.07.19 |

| [반도체소자] 14. FinFET (1) (0) | 2023.07.11 |

| [반도체소자] 13. Advanced MOSFET (0) | 2023.07.05 |

| [반도체소자] 12. SOI MOSFET (2) (0) | 2023.07.05 |