| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | ||||||

| 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| 16 | 17 | 18 | 19 | 20 | 21 | 22 |

| 23 | 24 | 25 | 26 | 27 | 28 | 29 |

| 30 | 31 |

- Short Channel Effect

- mechanism

- SK하이닉스

- Energy Band

- 선결함

- MOSFET

- feol

- DRAM

- 반도체공정

- high bandwidth memory

- 부피결함

- 양자역학

- finFET

- 반도체소자

- Threshold Voltage

- She

- Warpage

- effective mass

- Dynamic Random Access Memory

- HBM

- GIDL

- RCAT

- SOI MOSFET

- 반도체 8대공정

- Silicon on Insulator

- oxidation

- Punch through

- 반도체공학

- ion implantation

- 면접준비

- Today

- Total

반도체 공부 기록

[반도체소자] 14. FinFET (1) 본문

FinFET

FinFET은 SOI MOSFET과 마찬가지로 SHE(Short channel effect)를 개선하기 위해서 제안된 소자 구조입니다. FinFET의 Fin은 '상어 지느러미'라는 뜻으로 MOSFET의 채널을 Fin 형태로 만들고 Fin의 3면의 Gate으로 둘러 쌓은 형태를 가지는 FET입니다. Channel을 3면으로 제어하기 때문에 Gate controllability가 기존의 Planar MOSFET(2D MOSFET)에 비해 우수하여 SHE를 효과적으로 제어할 수 있습니다. 현재 개발되고 있는 MOSFET은 FinFET으로 기반으로 발전한 GAAFET입니다.

FinFET은 Planar MOSFET보다 Gate controllability가 우수하여 SHE를 효과적으로 통제할 수 있습니다. 따라서 FinFET은 Planar MOSFET보다 Subthreshold swing(Leakage current), Operation speed 특성이 우수합니다. 따라서 MOSFET의 개발은 Planar MOSFET(2D) → FinFET(3D) → GAA(Gate-All-Around)FET(4D) → MBC(Multi Bridge Channel)FET(4D)의 구조로 발전되고 있다. (MBCFET은 GAAFET에서 사용하는 Nanowire의 구조의 경우 표면적이 좁아 On-current의 크기가 작은 문제를 해결하기 위해 Nanosheet를 통해 표면적을 증가시킨 구조입니다.)

♭ FinFET

Planar MOSFET와 마찬가지로 FinFET도 Substrate를 SOI와 Bulk Si을 이용하여 제작하였습니다. (FD) SOI FinFET은 (FD) SOI MOSFET에서 소자 미세화에 따라 줄어드는 On-current를 Fin의 형태로 단면적을 늘려 극복했습니다. FinFET의 Effective channel length는 2Hfin+Wfin으로 Planar MOSFET보다 2Hfin만큼 증가하였습니다.

하지만 Effective channel length를 증가시키기 위해 Wfin을 증가시키면 Fin 영역에서 Gate의 영향이 미치지 않는 영역이 생겨 Performance가 감소합니다. 그래프를 참고하면 Fin width 증가에 따라서 SS(Subthreshold swing)은 증가하여 Ion/Ioff ratio가 감소합니다. MOSFET은 SHE를 효과적으로 제어하여 낮은 SS 값을 가져 우수한 Switch 특성을 가지고, 낮은 Threshold voltage를 통해 저전력 소자를 개발해야합니다. 따라서 FinFET은 Fin width를 감소시켜 SS 특성을 개선하고 Fin width 감소에 의한 단면적 손실은 Fin height를 증가시켜 보상합니다. Hfin/Wfin은 높을수록 우수한 특성을 가지겠지만, 여러 공정적은 이슈로 인해 어려움이 있습니다. (Fin 구조 형성을 위한 Anisotropic etch, Fin의 균일한 도핑 등)

SOI FinFET과 Bulk FinFET은 Threshold voltage, DIBL, SS(Subthreshold swing)은 유사한 특성을 가지고 있습니다. 하지만 지난 SOI MOSFET 포스팅에서 설명한 Self-heating 현상에 의해 소자의 온도가 증가하는 문제가 있었습니다. Bulk FinFET은 SOI FinFET과 다르게 Channel 영역에서 발생하는 열이 Substrate으로 방출될 수 있어, FinFET의 동작 전압 조건에서 Heat transfer 특성이 SOI 보다 Bulk에서 우수합니다. 이에 따라서 SOI FinFET과 Bulk FinFET 사이의 Performance의 차이는 무시할 수 있지만 SOI FinFET의 Heat transfer 특성에 의해 Bulk FinFET을 사용합니다.

♭ Natural length

FinFET이 Planar MOSFET에 비해 Gate controllability이 높아 SHE를 효과적으로 개선할 수 있음을 여러 가지 지표를 통해서 확인해보았습니다. Natural length를 통해서 FinFET이 Planar MOSFET 보다 Gate controllability가 우수한 이유를 수식적으로 알아보도록 하겠습니다.

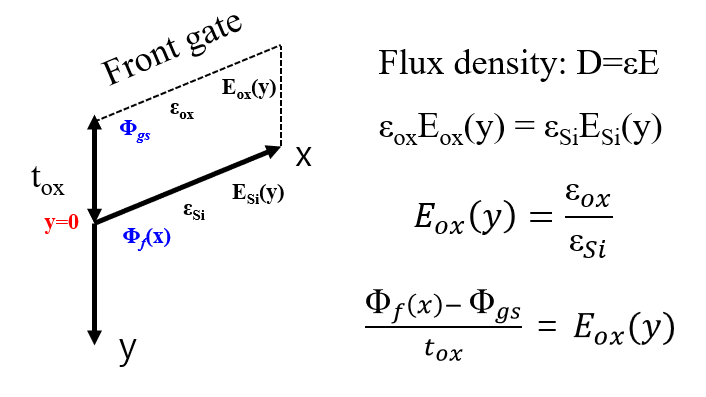

Single gate와 Double gate의 Natural length를 비교하여 Channel을 제어하는 Dimension에 따른 Gate controllability를 차이를 알아보겠습니다. SIngle gate의 경우 -y 방향으로 Front gate가 위치하고 +y 방향으로 BOX가 있습니다. Double gate의 경우는 -y 방향으로 Front gate가 위치하고 +y 방향으로는 Back gate가 있습니다.

Flux denisty는 연속한 물질에서는 일정한 값을 가지므로 εoxEox(y) = εSiESi(y)가 성립합니다. Possion's equation의 정의에 따라 전기장은 일정한 거리 사이의 포텐셜 차이(Potential difference)로 정의할 수 있습니다.

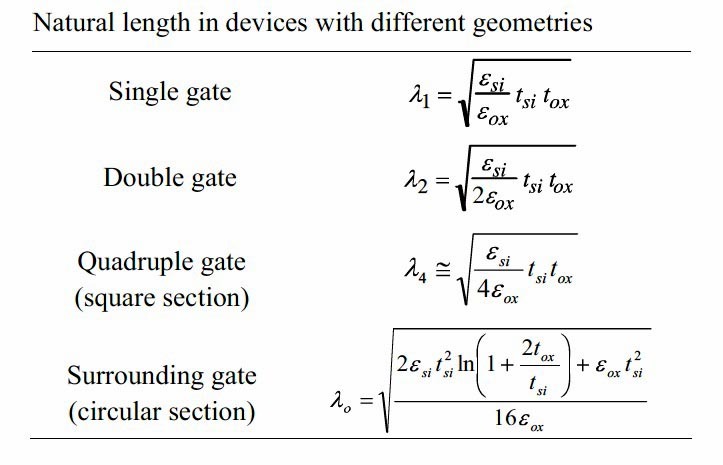

MOSFET은 전기장 성분이 3차원으로 고려해야 하기 때문에 Potential을 y에 관한 2차 함수(첫번째 수식)로 위와 같이 정의할 수 있습니다. 우선 Single gate SOI MOSFET에서 y=0은 Front gate의 Surface potential을 의미하고(두번째, 세번째 수식), y=tSi는 BOX 표면에서의 Surface potential을 의미합니다(네번째 수식). 일반적으로 BOX는 매우 두껍기 때문에 y=tSi에서의 Potential은 무시할 수 있습니다. 2가지 조건(세번째, 네번째 수식)에 의해 포텐셜을 위와 같이 정의할 수 있습니다(다섯번째 수식). 여기서 Natural length는 (포텐셜 차이 제외한) 계수의 역수의 제곱근으로 정의할 수 있습니다.

Double gate(DG) MOSFET의 경우에도 Potential을 y에 관한 2차 함수로 정의할 수 있습니다(첫번째 수식). DG MOSFET에서 y=0은 Front gate에서의 Surface potential을 의미하고(두번째, 세번째 수식), Single gate MOSFET가 달리 y=tSi은 Back gate에서의 Surface potential을 의미합니다(네번째 수식). DG MOSFET은 대칭 구조를 가지기 때문에 y=0과 y=tSi에서의 Surface potential의 크기는 같지만 부호가 반대입니다(네번째 수식). 마찬가지로 두가지 조건(세번째, 네번째 수식)을 이용하여 포텐셜을 위와 같이 정의할 수 있습니다(여섯번째 수식). 한편, Natural length는 Singe gate MOSFET의 경우보다 작아진 것을 확인할 수 있습니다(일곱번째 수식).

Natural length는 MOSFET의 형상학적 구조에 의존하는 값으로, SCE와 큰 상관관계가 있습니다. Natural length이 작은 값을 가질수록 SCE의 원인이 되는 수평방향의 전기장 성분이 작은 것을 의미합니다. DG MOSFET, FinFET이 Single gate MOSFET에 비해 Natural length가 작은 값을 가지게 되는데 Channel 영역을 높은 Dimension을 통해 통제할 수 있기 때문에 수평 방향으로의 전기장 성분이 작아지게 됩니다. 따라서 이번 포스팅에서 계속 언급한 것처럼 MOSFET의 개발 방향이 MOSFET의 Channel을 제어하는 Gate의 Dimension이 1D(Single gate MOSFET) → 2D(DG MOSFET) → 3D(FinFET) → 4D(GAAFET, MBCFET)와 같이 증가합니다.

<출처>

삼성전자 반도체이야기, "차세대 반도체를 위한 차세대 공정, 'GAA 구조' 트랜지스터" (2019).

J. H. Lee, "Bulk FinFETs: Design at 14nm Node and Key Characteristics", KAIST Research Series, (2015) 33-64.

N. E. I. Boukortt et al. "Effects of Varying the Fin Width, Fin Height, Gate Dielectric Material, and Gate Length on the DC and RF Performance of a 14-nm SOI FinFET Structure", Electronics, 11 (2022) 91.

A. Harb et al., "28-nm UTBB FD-SOI vs. 22-nm Tri-Gate FinFET Review: A Designer Guide - Part I", Circuit and Systems, 8 (2017) 93-110.

Y. C. Wu & Y. R. Jhan, "Gate-All-Around (GAA) NWFET with Lg = 10nm Simulation", 3D TCAD Simulation for CMOS Nanoelectric Devices, (2018) 211-238.

오류가 있다면 지적해주시면 감사하겠습니다 :)

'반도체소자' 카테고리의 다른 글

| [반도체소자] 16. DRAM (1) (0) | 2023.07.19 |

|---|---|

| [반도체소자] 15. FinFET (2) (0) | 2023.07.13 |

| [반도체소자] 13. Advanced MOSFET (0) | 2023.07.05 |

| [반도체소자] 12. SOI MOSFET (2) (0) | 2023.07.05 |

| [반도체 소자] 11. SOI MOSFET (1) (0) | 2023.07.04 |